Journal of Engineering Research and Reports

17(4): 39-43, 2020; Article no.JERR.61975 ISSN: 2582-2926

## Elimination of Smashed Ball Defect through Process and Design Improvement

Jonathan C. Pulido<sup>1</sup>, Rennier S. Rodriguez<sup>1</sup> and Frederick Ray I. Gomez<sup>1\*</sup>

<sup>1</sup>New Product Development and Introduction, STMicroelectronics, Inc., Calamba City, Laguna, 4027, Philippines.

### Authors' contributions

This work was carried out in collaboration among all authors. All authors read, reviewed, and approved the final manuscript.

### Article Information

DOI: 10.9734/JERR/2020/v17i417195 <u>Editor(s):</u> (1) Dr. Djordje Cica, University of Banja Luka, Bosnia and Herzegovina. <u>Reviewers:</u> (1) Derouiche Hassen, University of Carthage, Tunisia. (2) I. Dhanya, Mahatma Gandhi University, India. Complete Peer review History: <u>http://www.sdiarticle4.com/review-history/61975</u>

Original Research Article

Received 08 August 2020 Accepted 13 October 2020 Published 24 October 2020

### ABSTRACT

This paper presents the modification and improvement done on the wire clamp and top plate (WCTP) design to eliminate the bouncing effect of the silicon die that leads to smashed ball reject during the formation of wire. The protrusion of the unit on the vacuum hole produced movement and slight vibration that affects the consistency of wirebonding. Through changing the standard vacuum hole to micro-holes provides underneath support to the unit and eliminates the overhanging or protrusion during the formation of wire. The implementation of the micro-hole design reduced the defect parts per million (dppm) occurrence to zero.

Keywords: Assembly; smashed ball; WCTP; wirebond process.

### **1. INTRODUCTION**

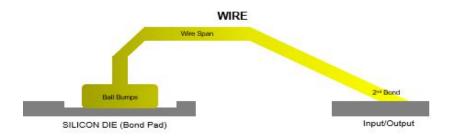

Wirebonding or wirebond is a process under semiconductor assembly wherein it directly

attached a semiconductor wire from the silicon die to the substrate/leadframes to create an electrical connectivity to the external printed circuit board (PCB).

\*Corresponding author: Email: frederick-ray.gomez@st.com, f.i.gomez@ieee.org;

Fig. 1. Wire structure

This technique of connecting the silicon die to the input/output (I/O) became popular due to growing demand for compact and smaller integrated circuit (IC) packaging like Quad-Flat No-Lead (QFN), Quad-Flat Packages (QFP) and Ball Grid Array (BGA) that has delicate structure of bonding pads. Note that with new and continuous technology trends and state-of-the-art platforms, challenges are inevitable [1-4].

The wire used is usually made either of gold or aluminum, with copper and silver wires added recently in semiconductor assembly manufacturing industry [5-6]. The typical wires can be attached using thermocompression method. This technique uses heat that is applied to the material to create a material softening synchronized to the application of pressure to mechanically form an intermetallic between two materials (bondpad to wire). Later development for wirebonding introduces ultrasonic principle together with thermocompression method which is mostly recommended for more delicate structure of bonding pads. In this technique, there is less pressure required and the formation of intermetallic structure is driven by the application of ultrasonic to the capillary.

In forming a complete cycle of wiring, a ball bumps were formed first on the capillary then it is attached to the bonding pads of the silicon die. Afterwards, the capillary moves to the defined I/O to attach the opposite end of the wire. This process is repeated until all bonding pads is connected to the defined location of I/O.

Since we are dealing with micron thick bonding pads, the wirebonding and visual inspection became critical and time consuming for the production personnel since it requires an appropriate inspection equipment to use for to the size of each bonding pad that usually ranges from 60 -150 microns. In addition, a silicon die is composed of several bonding pads. In this case,

manufacturing implemented proactive approach such as correlating the visual manifestation of the wire to the quality of bonding and wire structure.

This paper presents the improvement done on the consistency of ball bumps for thin silicon die through modifications of indirect material. The rearrangement of vacuum hole for wire clamp and top plate (WCTP) produces significant improvement in the visual integrity of the ball bumps and wiring.

### 2. LITERATURE REVIEW AND PROBLEM IDENTIFICATION

A typical assembly process flow for semiconductor IC package is illustrated in Fig. 2. Important to note that assembly process flow varies with the product and the technology [7-8]. The process in focus for this paper is wirebonding, as discussed earlier.

One of the existing defects for wire is smashed ball or when the ball bumps is bonded inconsistently as shown in Fig. 3. A smashed ball defect may produce bond pad cracks and might damage the internal array of connection of the silicon die. The manifestation of this defect signifies internal damage that might not be easily detected through series of inspection but greatly affects the functionality of the unit.

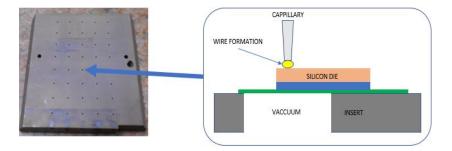

Process mapping suggested to investigate the relationship of the vacuum hole of the insert to the occurrence of intermittent smashed ball on the units. From the simulation and placement study, a protrusion of the unit from the vacuums hole is possible.

Bouncing effect is observed during the formation of wire or when the capillary applies force to the silicon die (bonding pad) during the formation of intermetallic between wire and pads, Gomez et al.; JERR, 17(4): 39-43, 2020; Article no.JERR.61975

### Fig. 2. Assembly process flow

Newly setup bumps

Sustaining

Fig. 3. Smashed ball

Fig. 4. Bouncing during wire formation

As depicted in Fig. 4. The unit that protrudes to the vacuum holes has no underneath support to the applied force of the capillary that leads to slightly push the unit against the vacuum hole. Since the unit (silicon die) is not stable during this sequence, an inconsistent formation of ball bumps may appear.

# 3. PROCESS AND DESIGN IMPROVEMENT

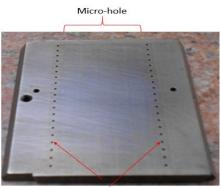

The focused of the optimization of the WCTP is to eliminate the occurrence of smashed ball through re-designing the vacuum hole of the insert. An insert with the combination of microholes and standard vacuum hole design is shown in Fig. 5.

The micro-hole applies vacuum to the unit that will be wirebonded and standard vacuum hole on

each side is to hold the leadframe or substrate from moving. This design of insert is applicable for "panel" and single column design setup of leadframe. For panel setup, the length and width of the array of micro-holes should be equal to the number of rows per panel and the standard vacuum hole is incorporated to the before and after the panel. For single column, micro-hole is assigned particular to row that will be bonded and the standard vacuum hole is incorporated to the nearest column.

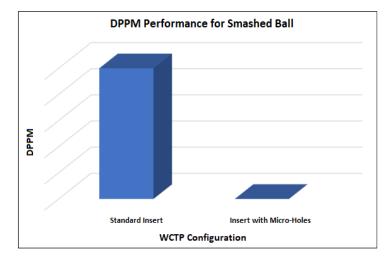

Measurement of defect before and after the implementation of the improved design of insert is given in Fig. 6.

Standard design of insert produced around 25k defect parts per million (dppm) while the improved design on insert shows no smashed ball defect.

#### Gomez et al.; JERR, 17(4): 39-43, 2020; Article no.JERR.61975

Standard Vacuum

Fig. 6. Dppm performance comparison showing total reduction of smashed ball dppm

### 4. CONCLUSION AND RECOMMENDA-TIONS

Smashed ball elimination was successfully realized through the process and design improvement focused in the WCTP. The rearrangement and introduction of micro-holes in the WCTP design produced a 100% improvement in the smash ball defect reduction with the defect occurrence actually eliminated.

The technique in WCTP shared in this study could be used for future works on other semiconductor devices with similar configuration. Comparison of existing works and other studies should also be included for added analysis. Important to note that continuous process improvement is imperative to sustain the high quality performance of semiconductor products and its assembly manufacturing. Studies and learnings shared in [9-11] are helpful in reinforcing robustness and optimization of assembly processes focused in wirebonding.

### ACKNOWLEDGEMENT

The authors would like to thank the Management Team (MT) and the New Product Development & Introduction (NPD-I) team for the constant support.

### **COMPETING INTERESTS**

Authors have declared that no competing interests exist.

### REFERENCES

1. Liu Y, et al. Trends of power electronic packaging and modeling. 10th Electronics Packaging Technology Conference, Singapore; December 2008.

- Saha S. Emerging business trends in the semiconductor industry. Proceedings of PICMET '13: Technology Management in the IT-Driven Services (PICMET). USA. 2013; 2744-2748.

- Yeap LL. Meeting the assembly challenges in new semiconductor packaging trend. 34th IEEE/CPMT International Electronic Manufacturing Technology Symposium (IEMT). Malaysia. 2010; 1-5.

- 4. Sumagpang Jr. A and Rada A. A systematic approach in optimizing critical processes of high density and high complexity new scalable device in MAT29 risk production using state-of-the-art platforms. Presented at the 22nd ASEMEP Technical Symposium, Philippines; June 2012.

- Lall P, et al. Reliability of copper, gold, silver, and pcc wirebonds subjected to harsh environment. IEEE 68th Electronic Components and Technology Conference (ECTC). USA. 2018; 724-734.

- 6. Tan CE, et al. Challenges of ultimate ultrafine pitch process with gold wire & copper

wire in QFN packages. 36th International Electronics Manufacturing Technology Conference. Malaysia. 2014; 1-5.

- 7. Harper C. Electronic packaging and interconnection handbook. 4th ed. McGraw-Hill Education, USA; 2004.

- 8. Geng H. Semiconductor manufacturing handbook. 2nd ed. McGraw-Hill Education, USA; 2017.

- 9. Moreno A, et al. Wire shorting elimination through wirebond process optimization of semiconductor sensor device. Journal of Engineering Research and Reports. 2020; 13(4):10-14.

- Pulido J, et al. Wirebond process improvement with enhanced stand-off bias wire clamp and top plate. Journal of Engineering Research and Reports. 2020; 9(3):1-4.

- 11. Sumagpang Jr. A, et al. Package design improvement for wire shorting resolution. Journal of Engineering Research and Reports. 2020; 11(2):41-44.

© 2020 Gomez et al.; This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Peer-review history: The peer review history for this paper can be accessed here: http://www.sdiarticle4.com/review-history/61975